Digital Logic Design Remedial MCQs 1

Q: What is the minimum number of two-input NAND gates used to perform the function of two input OR gate ?

- A: three

- B: one

- C: two

- D: None

Q: In which of the following gates, the output is 1, if and only if at least one input is 1?

- A: NOR

- B: OR

- C: AND

- D: NAND

Q: Which one of the following will give the sum of full adders as output ?

- A: Three bit parity checker

- B: Three bit counter

- C: Three bit comparator

- D: Three point majority circuit

Q: Which of the following statements is wrong ?

- A: Fan-in of a gate is always equal to fan-out of the same gate

- B: Operating speed is the maximum frequency at which digital data can be applied to a gate

- C: Noise immunity is the amount of noise which can be applied to the input of a gate without causing the gate to change state

- D: Propagation delay is the time required for a gate to change its state

Q: The time required for a gate or inverter to change its state is called ...

- A: Decay time

- B: Rise time

- C: Propagation time

- D: Charging time

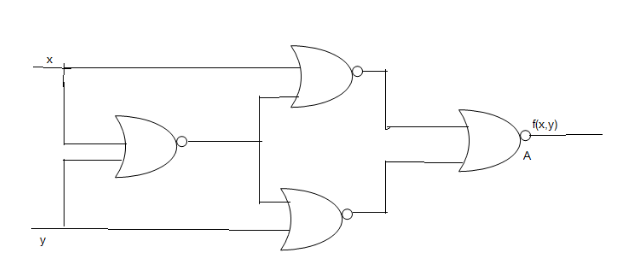

Q: Identify the logic function performed by the circuit shown in the given figure

- A: Exclusive OR

- B: NAND

- C: Exclusive NOR

- D: NOR

Q: A one-to-four line demultiplexer is to be implemented using a memory. How many bits must each word have

- A: 2 bit

- B: 1 bits

- C: 4 bits

- D: 8 bits

Q: How many full adders are required to construct an m-bit parallel adder

- A: m-1

- B: m/2

- C: m+1

- D: m

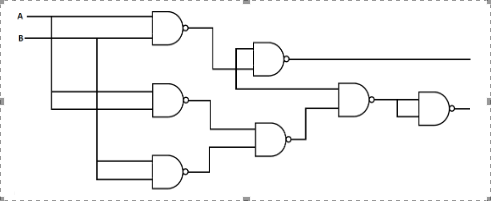

Q: What logic function is performed by the circuit shown below?

- A: Half adder

- B: Full adder

- C: Ring counter

- D: Ripple counter

Q: The dual of the switching function x + yz is:

- A: x(y+z)

- B: x̄ + ȳz̄

- C: x̄(ȳ + z̄)

- D: x+yz